时间:2022-01-13 14:58:01来源:

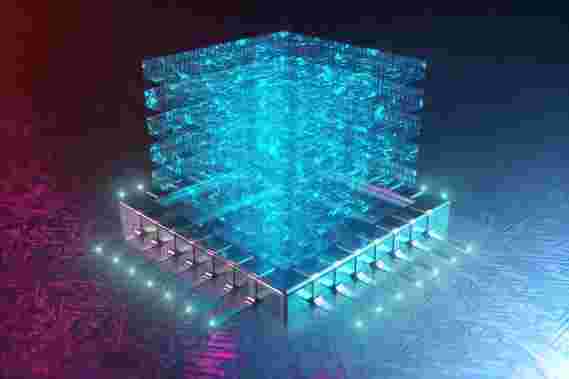

用于计算机处理器的硅集成电路,在二维阵列中,在单个芯片上接近单个芯片上的晶体管的最大可行性密度。

现在,密歇根大学的工程师团队直接在最先进的硅芯片上堆叠了第二层晶体管。

他们建议他们的设计可以消除对高电压信号之间的第二芯片的需要,该电压在低压处理芯片和高压用户界面之间存在。

“我们的方法可以在较小,更轻的方案中实现更好的性能,”电气工程与计算机科学与项目领导者副教授Becky Peterson表示。

摩尔的法律认为,每美元的计算能力大约每两年加倍。由于硅晶体管的尺寸缩小,以变得更实惠和功效效率,它们的操作的电压也在下降。

较高的电压会损坏越来越小的晶体管。因此,最先进的处理芯片与高压用户界面组件(例如触摸板和显示驱动器)不兼容。这些需要在更高的电压下运行,以避免诸如假触摸信号或太低的亮度设置等效果。

“为了解决这个问题,我们正在将不同类型的设备与3D中的硅电路集成在一起,并且这些设备允许您进行硅晶体管不能做的事情,”Peterson说。

因为第二层晶体管可以处理更高的电压,所以它们基本上给出每个硅晶体管其自己的解释器用于与外界交谈。这绕过目前使用最先进的处理器使用额外的芯片来转换处理器和接口设备之间的信号 - 或者使用以更高电压运行的低档处理器转换信号。

“这使得能够更紧凑的芯片,而不是只有硅的功能,”Youngbae Son说,纸张的第一作者和U-M电脑工程最近的博士毕业生博士学位。

彼得森的团队通过使用不同种类的半导体来管理这一点,称为无定形金属氧化物。为了将该半导体层应用于硅芯片而不会损坏它,它们用含锌和锡的溶液覆盖了芯片,并使其旋转以产生均匀的涂层。

接下来,他们简单地烘焙芯片以使其烘干。它们重复了该方法使一层锌 - 氧化锡层约75纳米厚 - 约一数千分之一的人毛的厚度。在最终烘烤期间,金属在空气中粘合到氧气中,产生一层锌 - 氧化锡。

该团队使用锌锡氧化膜来制造薄膜晶体管。这些晶体管可以处理比下方的硅更高的电压。然后,团队测试了底层硅芯片并确认它仍然有效。

为了用硅芯片制造有用的电路,所需的锌 - 氧化锡晶体管需要与下面的硅晶体管完全通信。该团队通过使用锌 - 氧化锌:垂直薄膜二极管和肖特基门控晶体管加入两个更多的电路元件来实现这一点。

两种锌 - 锡氧化物晶体管连接在一起以制造逆变器,在硅芯片使用的低电压和其他部件使用的较高电压之间转换。二极管用于将无线信号转换为硅晶体管的有用直流电源。

这些演示铺平了融合摩尔定律的硅集成电路,使氧化物电子器件的模拟和数字优势融入硅晶体管。

###

参考:“使用解决方案过程的高压薄膜电子对低压综合电路的单片集成”由年轻人儿子,布拉德弗罗斯特,Yundai Zhao和Rebecca L. Peterson,2019年11月18日,Nature Electronics.doi:

10.1038 / s41928-019-0316-0

该研究由国防高级研究项目代理代理裁决提供资金。

声明:文章仅代表原作者观点,不代表本站立场;如有侵权、违规,可直接反馈本站,我们将会作修改或删除处理。

图文推荐

2022-01-13 14:58:00

2022-01-13 13:58:00

2022-01-13 12:58:00

2022-01-13 11:58:00

2022-01-13 10:58:00

2022-01-13 09:58:00

热点排行

精彩文章

2022-01-13 13:58:02

2022-01-13 12:58:02

2022-01-13 11:58:02

2022-01-13 10:58:02

2022-01-13 09:58:02

2022-01-13 08:58:05

热门推荐