时间:2021-11-10 12:58:03来源:

麻省理工学院的工程师迈出了设计一种使用较大的无人机电脑的一小部分的计算机芯片的第一步,并为瓶颈的无人机量身定制。

麻省理工学院的工程师团队开发了一种设计高效的计算机芯片的方法可能会使地面上的微型智能玻璃器皿。

近年来,工程师已经致力于收缩无人机技术,建造飞行原型,这些原型是大黄蜂的尺寸,并装载了甚至更细的传感器和摄像机。到目前为止,他们已经设法缩小了无人机的几乎所有部分,除了整个操作的大脑 - 计算机芯片。

标准计算机芯片用于Quadcoptors和其他类似尺寸的无级的稳定性从摄像机和传感器处理大量的流式流数据,并将其解释为飞行,以自主地引导无人机的音高,速度和轨迹。为此,这些计算机在10到30瓦的功率之间使用,由电池提供,这些电池将重大缩小更小的蜂窝纱。

现在,麻省理工学院的工程师已经迈出了设计一种使用较大的无人机计算机的一小部分的计算机芯片的第一步,并为瓶颈的无人机量身定制。他们将提出一种新的方法和设计,他们在机器人学上称之为“Navion”:科学与系统会议,本周在麻省理工学院举行。

该团队由Sertac Karaman领导,1948年职业发展副教授的航空航天助理教授,MIT电气工程系和计算机科学系的副教授Vivienne Sze,开发了一种低功耗算法,串联折叠硬件,创建专用计算机芯片。

他们的作品的主要贡献是设计芯片硬件的新方法和在芯片上运行的算法。“传统上,设计了一种算法,您将其丢弃到硬件人员以如何将算法映射到硬件,”Sze说。“但是我们通过将硬件和算法设计在一起,我们可以实现更大量的节能。”

“我们发现这种新的编程机器人的方法,涉及共同思考硬件和算法,是将它们缩小的钥匙,”卡拉曼说。

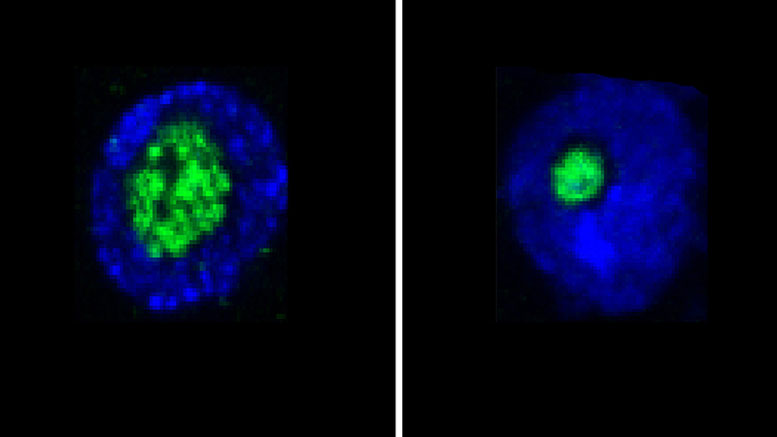

新芯片处理每秒20帧的流映射图像,并自动执行命令以调整空间中的无人机的方向。流线型芯片执行所有这些计算,同时使用低于2瓦的电力 - 使其比当前无人机嵌入式芯片更有效。

卡拉曼说,球队的设计是迈向工程的第一步“可以自行飞行的最小智能无人机”。他最终设想了灾难 - 反应和搜救任务,其中昆虫尺寸的无人机在紧密的空间中捕获,检查折叠结构或寻找被困的杀戮。Karaman还预计在消费电子产品中的新用途。

“想象一下,购买可以与手机集成的瓶颈大小的无人机,你可以把它拿出来贴在你的手掌中,”他说。“如果你抬起一点点,它会感觉到这一点,并开始飞行和电影。然后你再次张开你的手,它会落在你的手掌上,你可以将该视频上传到手机并与他人分享。“

卡拉曼和苏立泽的共同作者是郑东张和艾瑞米曼的研究生,以及研究科学家卢卡卡隆。

从地上起来

目前的Minidrone原型足够小,可以适合一个人的指尖,非常轻盈,需要只有1瓦的电力从地面抬起。他们随附的相机和传感器使用额外的一半瓦特来操作。

“缺失的部分是计算机 - 我们不能在尺寸和力量方面融合它们,”卡拉曼说。“我们需要小型化计算机并使它们低功耗。”

该集团迅速意识到传统的芯片设计技术可能不会产生足够小的芯片,并提供了所需的处理能力,以智能地飞行小型自主无人机。

“随着晶体管的较小,效率和速度已经提高,但这已经放慢了,现在我们必须提出专门的硬件来提高效率,”Sze说。

研究人员决定从地上建立一个专业的芯片,开发算法来处理数据,以及硬件在串联中执行数据处理。

调整一条公式

具体而言,研究人员对通常用于确定无人机的“自我运动”或在太空中的位置的意识的情况下进行了略可的算法。然后,它们在现场可编程门阵列(FPGA)上实现了各种版本的算法,这是一个非常简单的可编程芯片。为了形成此过程,他们开发了一种称为迭代拆分协同设计的方法,可以在降低功耗和门的数量的同时,可以取得准确性的右平衡。

典型的FPGA由数十万个断开连接的门组成,研究人员可以以所需的模式连接以创建专用计算元素。通过共同设计减少盖茨允许团队选择具有更少门的FPGA芯片,从而节省了大量的电力。

“如果我们不需要某个逻辑或内存过程,我们就不会使用它们,并且节省了很多功率,”Karaman解释说。

每次研究人员调整自我运动算法时,它们都会将该版本映射到FPGA的盖茨并将芯片连接到电路板。然后,它们从标准无人机数据集中馈送芯片数据 - 从其他人进行的以前的无人机飞行实验中的流媒体图像和加速度计测量的累积,并为机器人社区提供。

“这些实验也在运动捕获室中进行,所以你确切地知道无人机在哪里,我们在事实之后使用所有这些信息,”卡拉曼说。

记忆储蓄

对于在FPGA芯片上实现的算法的每个版本,研究人员观察到芯片所消耗的功率量,因为它处理了输入数据并估计其在空间中的结果位置。

该团队最有效的设计在每秒20帧时处理图像,并准确地估计了空间中的无人机的方向,同时消耗不到2瓦的电力。

节能部分地从修改到存储在芯片中的内存量。SZE和她的同事发现,他们能够缩小过程所需的数据量,同时仍然实现相同的结果。结果,芯片本身能够存储更少的数据并消耗更少的功率。

“内存在力量方面非常昂贵,”Sze说。“由于我们在飞行的计算中,我们一旦收到芯片上的任何数据,我们就会尽可能多地处理,因此我们可以立即丢弃它,这使我们能够保持非常少量的芯片上的内存而不访问芯片内存,这更昂贵。“

通过这种方式,与用于无人机的典型嵌入式计算机芯片相比,该团队能够将芯片的内存存储器减少到2兆字节,而无需使用片外存储器,其使用几个千兆字节的芯片内存。

“任何您可以减少电源的方式,这样您就可以降低电池尺寸或延长电池寿命,更好,”Sze说。

今年夏天,该团队将FPGA芯片将FPGA芯片安装到无人机上以测试其在飞行中的性能。最终,团队计划在特定于应用专用的集成电路或ASIC上实现优化的算法,更专用的硬件平台,允许工程师直接在芯片上设计特定类型的门。

“我们认为我们可以将此降至几百毫瓦,”卡拉曼说。“通过这个平台,我们可以做各种优化,允许巨大的省电。”

这项研究部分受到了科学研究和国家科学基金会空军办公室的支持。

出版物:

声明:文章仅代表原作者观点,不代表本站立场;如有侵权、违规,可直接反馈本站,我们将会作修改或删除处理。

图文推荐

2021-11-10 12:58:03

2021-11-10 11:58:02

2021-11-10 10:58:03

2021-11-10 09:58:02

2021-11-10 08:58:02

2021-11-09 19:58:00

热点排行

精彩文章

2021-11-10 11:58:04

2021-11-10 10:58:13

2021-11-10 09:58:05

2021-11-10 08:58:04

2021-11-09 19:58:02

2021-11-09 18:58:02

热门推荐